5. 封装信息¶

5.2. 引脚属性¶

[1]: 芯片封装引脚序号。

[2]: 芯片封装引脚名称。

[3]: 类型,指示信号方向。

I —— 输入;

O —— 输出;

I/O —— 输入/输出;

OD —— 开漏;

A —— 模拟;

AI —— 模拟输入;

AO —— 模拟输出;

P —— 电源;

G —— 地;

[4]:引脚复位状态,PU 指上拉,PD 指下拉,Z 指高阻态。

[5]:PU/PD 表示内部存在上下拉电阻,且上下拉电阻可通过软件开启或关闭。

[6]:默认驱动能力大小。GPIO 默认驱动能力20mA,最大50mA。

[7]:电源供电。

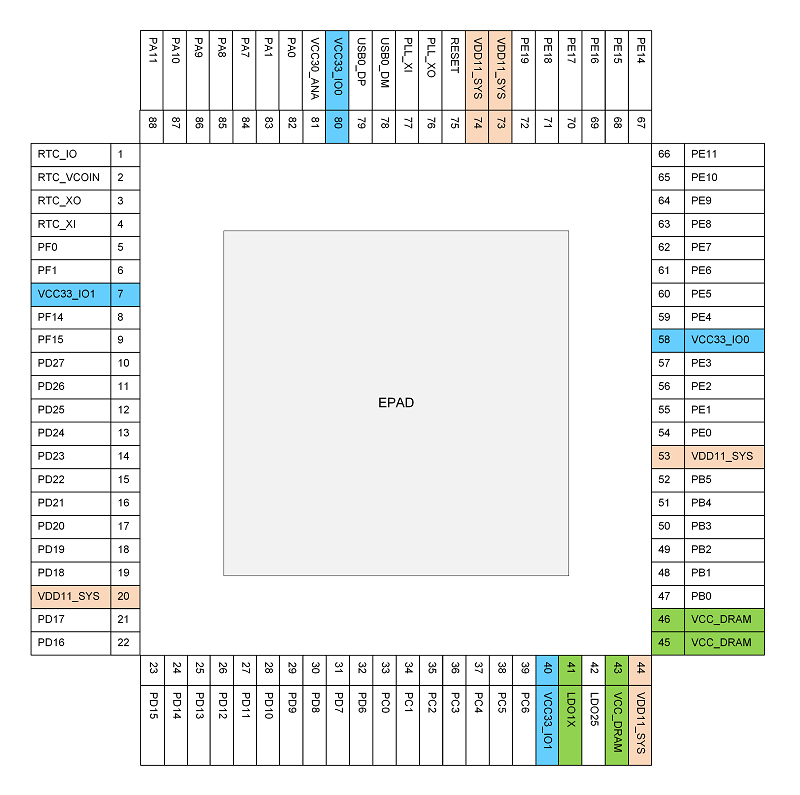

5.2.1. D211BB/D211BC QFN88¶

引脚[1]

名称[2]

类型[3]

复位状态[4]

上下拉[5]

默认驱动(mA)[6]

供电[7]

GPIO A

82

PA0

I/O

Z

PU/PD

20

VCC33_IO0

83

PA1

I/O

Z

PU/PD

20

VCC33_IO0

84

PA7

I/O

Z

PU/PD

20

VCC33_IO0

85

PA8

I/O

Z

PU/PD

20

VCC33_IO0

86

PA9

I/O

Z

PU/PD

20

VCC33_IO0

87

PA10

I/O

Z

PU/PD

20

VCC33_IO0

88

PA11

I/O

Z

PU/PD

20

VCC33_IO0

GPIO B

47

PB0

I/O

Z

PU/PD

20

VCC33_IO0

48

PB1

I/O

Z

PU/PD

20

VCC33_IO0

49

PB2

I/O

Z

PU/PD

20

VCC33_IO0

50

PB3

I/O

Z

PU/PD

20

VCC33_IO0

51

PB4

I/O

Z

PU/PD

20

VCC33_IO0

52

PB5

I/O

Z

PU/PD

20

VCC33_IO0

GPIO C

33

PC0

I/O

Z

PU/PD

20

VCC33_IO1

34

PC1

I/O

Z

PU/PD

20

VCC33_IO1

35

PC2

I/O

Z

PU/PD

20

VCC33_IO1

36

PC3

I/O

Z

PU/PD

20

VCC33_IO1

37

PC4

I/O

Z

PU/PD

20

VCC33_IO1

38

PC5

I/O

Z

PU/PD

20

VCC33_IO1

39

PC6

I/O

Z

PU/PD

20

VCC33_IO1

GPIO D

32

PD6

I/O

Z

PU/PD

20

VCC33_IO1

31

PD7

I/O

Z

PU/PD

20

VCC33_IO1

30

PD8

I/O

Z

PU/PD

20

VCC33_IO1

29

PD9

I/O

Z

PU/PD

20

VCC33_IO1

28

PD10

I/O

Z

PU/PD

20

VCC33_IO1

27

PD11

I/O

Z

PU/PD

20

VCC33_IO1

26

PD12

I/O

Z

PU/PD

20

VCC33_IO1

25

PD13

I/O

Z

PU/PD

20

VCC33_IO1

24

PD14

I/O

Z

PU/PD

20

VCC33_IO1

23

PD15

I/O

Z

PU/PD

20

VCC33_IO1

22

PD16

I/O

Z

PU/PD

20

VCC33_IO1

21

PD17

I/O

Z

PU/PD

20

VCC33_IO1

19

PD18

I/O

Z

PU/PD

20

VCC33_IO1

18

PD19

I/O

Z

PU/PD

20

VCC33_IO1

17

PD20

I/O

Z

PU/PD

20

VCC33_IO1

16

PD21

I/O

Z

PU/PD

20

VCC33_IO1

15

PD22

I/O

Z

PU/PD

20

VCC33_IO1

14

PD23

I/O

Z

PU/PD

20

VCC33_IO1

13

PD24

I/O

Z

PU/PD

20

VCC33_IO1

12

PD25

I/O

Z

PU/PD

20

VCC33_IO1

11

PD26

I/O

Z

PU/PD

20

VCC33_IO1

10

PD27

I/O

Z

PU/PD

20

VCC33_IO1

GPIO E

54

PE0

I/O

Z

PU/PD

20

VCC33_IO0

55

PE1

I/O

Z

PU/PD

20

VCC33_IO0

56

PE2

I/O

Z

PU/PD

20

VCC33_IO0

57

PE3

I/O

Z

PU/PD

20

VCC33_IO0

59

PE4

I/O

Z

PU/PD

20

VCC33_IO0

60

PE5

I/O

Z

PU/PD

20

VCC33_IO0

61

PE6

I/O

Z

PU/PD

20

VCC33_IO0

62

PE7

I/O

Z

PU/PD

20

VCC33_IO0

63

PE8

I/O

Z

PU/PD

20

VCC33_IO0

64

PE9

I/O

Z

PU/PD

20

VCC33_IO0

65

PE10

I/O

Z

PU/PD

20

VCC33_IO0

66

PE11

I/O

Z

PU/PD

20

VCC33_IO0

67

PE14

I/O

Z

PU/PD

20

VCC33_IO0

68

PE15

I/O

Z

PU/PD

20

VCC33_IO0

69

PE16

I/O

Z

PU/PD

20

VCC33_IO0

70

PE17

I/O

Z

PU/PD

20

VCC33_IO0

71

PE18

I/O

Z

PU/PD

20

VCC33_IO0

72

PE19

I/O

Z

PU/PD

20

VCC33_IO0

GPIO F

5

PF0

I/O

Z

PU/PD

20

VCC33_IO1

6

PF1

I/O

Z

PU/PD

20

VCC33_IO1

8

PF14

I/O

Z

PU/PD

20

VCC33_IO1

9

PF15

I/O

Z

PU/PD

20

VCC33_IO1

RTC

1

RTC_IO

OD

-

-

-

-

2

RTC_VCOIN

P

-

-

-

-

3

RTC_XO

O

-

-

-

-

4

RTC_XI

I

-

-

-

-

PLL

75

RESET

I

-

-

-

-

76

PLL_XO

O

-

-

-

-

77

PLL_XI

I

-

-

-

-

USB

78

USB0_DM

A

-

-

-

-

79

USB0_DP

A

Power

58,80

VCC33_IO0

P

-

-

-

-

7,40

VCC33_IO1

P

-

-

-

-

81

VCC30_ANA

P

-

-

-

-

42

LDO25

P

-

-

-

-

41

LDO1X

P

-

-

-

-

43,45,46

VCC_DRAM

P

-

-

-

-

20,44,53,73,74

VDD11_SYS

P

-

-

-

-

89

GND

P

-

-

-

-

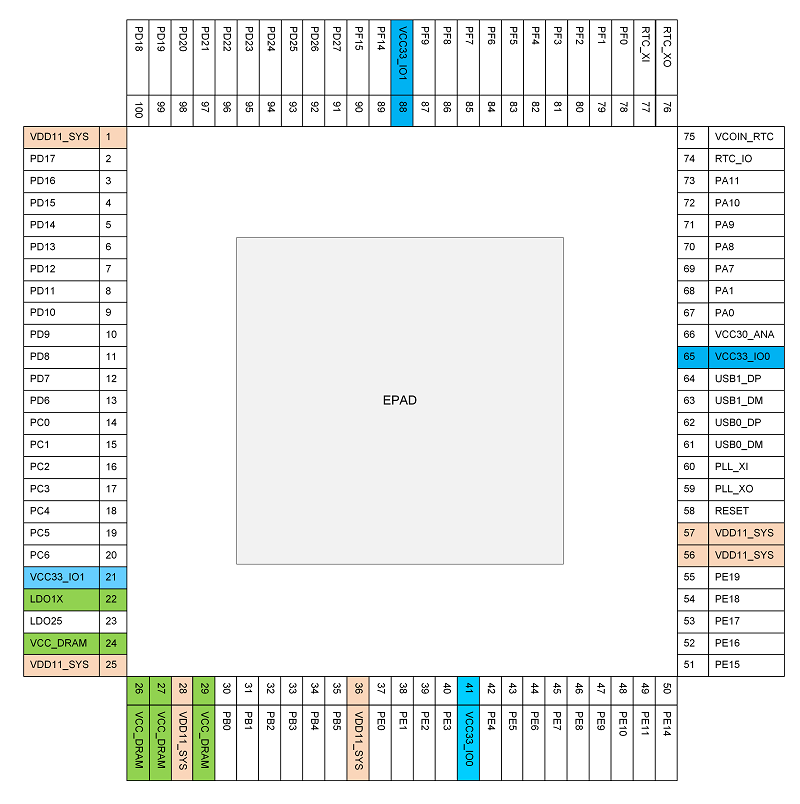

5.2.2. D211DB/D211DC QFN100¶

引脚[1]

名称[2]

类型[3]

复位状态[4]

上下拉[5]

默认驱动(mA)[6]

供电[7]

GPIOA

67

PA0

I/O

Z

PU/PD

20

VCC33_IO0

68

PA1

I/O

Z

PU/PD

20

VCC33_IO0

69

PA7

I/O

Z

PU/PD

20

VCC33_IO0

70

PA8

I/O

Z

PU/PD

20

VCC33_IO0

71

PA9

I/O

Z

PU/PD

20

VCC33_IO0

72

PA10

I/O

Z

PU/PD

21

VCC33_IO0

73

PA11

I/O

Z

PU/PD

20

VCC33_IO0

GPIO B

30

PB0

I/O

Z

PU/PD

20

VCC33_IO0

31

PB1

I/O

Z

PU/PD

20

VCC33_IO0

32

PB2

I/O

Z

PU/PD

20

VCC33_IO0

33

PB3

I/O

Z

PU/PD

20

VCC33_IO0

34

PB4

I/O

Z

PU/PD

20

VCC33_IO0

35

PB5

I/O

Z

PU/PD

20

VCC33_IO0

GPIO C

14

PC0

I/O

Z

PU/PD

20

VCC33_IO1

15

PC1

I/O

Z

PU/PD

20

VCC33_IO1

16

PC2

I/O

Z

PU/PD

20

VCC33_IO1

17

PC3

I/O

Z

PU/PD

20

VCC33_IO1

18

PC4

I/O

Z

PU/PD

20

VCC33_IO1

19

PC5

I/O

Z

PU/PD

20

VCC33_IO1

20

PC6

I/O

Z

PU/PD

20

VCC33_IO1

GPIO D

13

PD6

I/O

Z

PU/PD

20

VCC33_IO1

12

PD7

I/O

Z

PU/PD

20

VCC33_IO1

11

PD8

I/O

Z

PU/PD

20

VCC33_IO1

10

PD9

I/O

Z

PU/PD

20

VCC33_IO1

9

PD10

I/O

Z

PU/PD

20

VCC33_IO1

8

PD11

I/O

Z

PU/PD

20

VCC33_IO1

7

PD12

I/O

Z

PU/PD

20

VCC33_IO1

6

PD13

I/O

Z

PU/PD

20

VCC33_IO1

5

PD14

I/O

Z

PU/PD

20

VCC33_IO1

4

PD15

I/O

Z

PU/PD

20

VCC33_IO1

3

PD16

I/O

Z

PU/PD

20

VCC33_IO1

2

PD17

I/O

Z

PU/PD

20

VCC33_IO1

100

PD18

I/O

Z

PU/PD

20

VCC33_IO1

99

PD19

I/O

Z

PU/PD

20

VCC33_IO1

98

PD20

I/O

Z

PU/PD

20

VCC33_IO1

97

PD21

I/O

Z

PU/PD

20

VCC33_IO1

96

PD22

I/O

Z

PU/PD

20

VCC33_IO1

95

PD23

I/O

Z

PU/PD

20

VCC33_IO1

94

PD24

I/O

Z

PU/PD

20

VCC33_IO1

93

PD25

I/O

Z

PU/PD

20

VCC33_IO1

92

PD26

I/O

Z

PU/PD

20

VCC33_IO1

91

PD27

I/O

Z

PU/PD

20

VCC33_IO1

GPIO E

37

PE0

I/O

Z

PU/PD

20

VCC33_IO0

38

PE1

I/O

Z

PU/PD

20

VCC33_IO0

39

PE2

I/O

Z

PU/PD

20

VCC33_IO0

40

PE3

I/O

Z

PU/PD

20

VCC33_IO0

42

PE4

I/O

Z

PU/PD

20

VCC33_IO0

43

PE5

I/O

Z

PU/PD

20

VCC33_IO0

44

PE6

I/O

Z

PU/PD

20

VCC33_IO0

45

PE7

I/O

Z

PU/PD

20

VCC33_IO0

46

PE8

I/O

Z

PU/PD

20

VCC33_IO0

47

PE9

I/O

Z

PU/PD

20

VCC33_IO0

48

PE10

I/O

Z

PU/PD

20

VCC33_IO0

49

PE11

I/O

Z

PU/PD

20

VCC33_IO0

50

PE14

I/O

Z

PU/PD

20

VCC33_IO0

51

PE15

I/O

Z

PU/PD

20

VCC33_IO0

52

PE16

I/O

Z

PU/PD

20

VCC33_IO0

53

PE17

I/O

Z

PU/PD

20

VCC33_IO0

54

PE18

I/O

Z

PU/PD

20

VCC33_IO0

55

PE19

I/O

Z

PU/PD

20

VCC33_IO0

GPIO F

78

PF0

I/O

Z

PU/PD

20

VCC33_IO1

79

PF1

I/O

Z

PU/PD

20

VCC33_IO1

80

PF2

I/O

Z

PU/PD

20

VCC33_IO1

81

PF3

I/O

Z

PU/PD

20

VCC33_IO1

82

PF4

I/O

Z

PU/PD

20

VCC33_IO1

83

PF5

I/O

Z

PU/PD

20

VCC33_IO1

84

PF6

I/O

Z

PU/PD

20

VCC33_IO1

85

PF7

I/O

Z

PU/PD

20

VCC33_IO1

86

PF8

I/O

Z

PU/PD

20

VCC33_IO1

87

PF9

I/O

Z

PU/PD

20

VCC33_IO1

89

PF14

I/O

Z

PU/PD

20

VCC33_IO1

90

PF15

I/O

Z

PU/PD

20

VCC33_IO1

RTC

74

RTC_IO

OD

-

-

-

-

75

RTC_VCOIN

P

-

-

-

-

76

RTC_XO

O

-

-

-

-

77

RTC_XI

I

-

-

-

-

PLL

58

RESET

I

-

-

-

-

59

PLL_XO

O

-

-

-

-

60

PLL_XI

I

-

-

-

-

USB

61

USB0_DM

A

-

-

-

-

62

USB0_DP

A

63

USB1_DM

A

-

-

-

-

64

USB1_DP

A

-

-

-

-

Power

41,65

VCC33_IO0

P

-

-

-

-

21,88

VCC33_IO1

P

-

-

-

-

66

VCC30_ANA

P

-

-

-

-

23

LDO25

P

-

-

-

-

22

LDO1X

P

-

-

-

-

24,26,27,29

VCC_DRAM

P

-

-

-

-

1,25,28,36,56,57

VDD11_SYS

P

-

-

-

-

101

GND

P

-

-

-

-

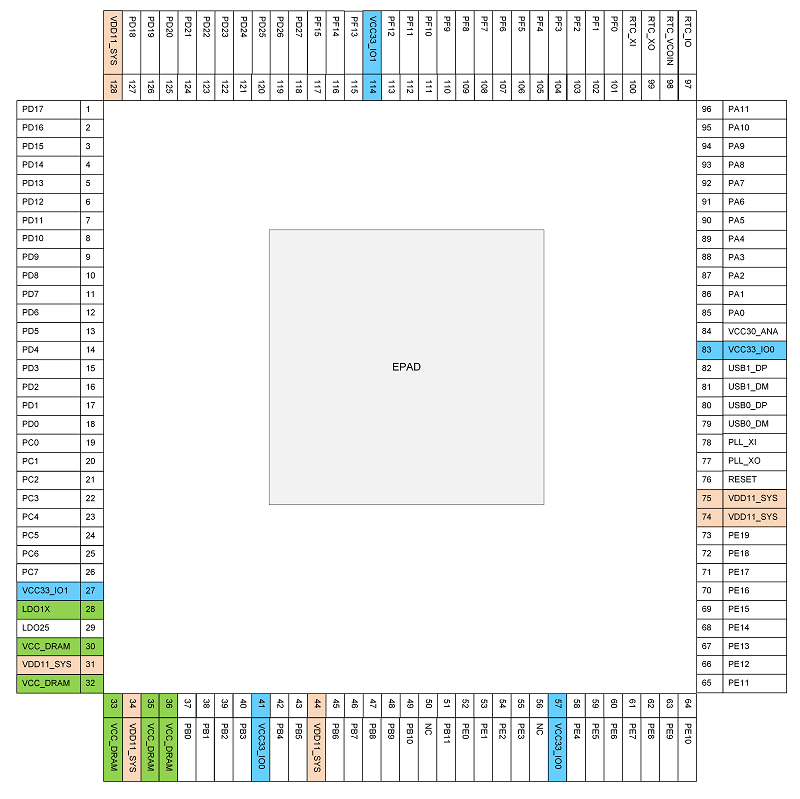

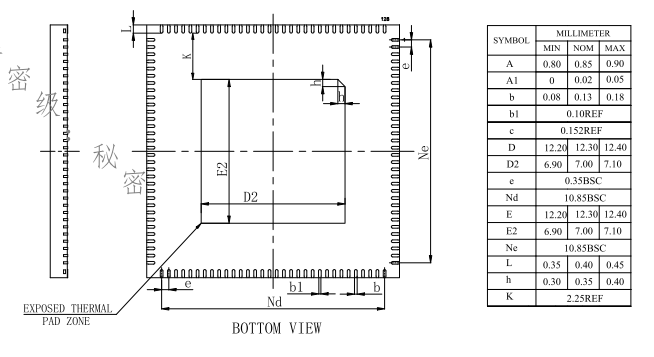

5.2.3. D213EC QFN128¶

引脚[1]

名称[2]

类型[3]

复位状态[4]

上下拉[5]

默认驱动(mA)[6]

供电[7]

GPIOA

85

PA0

I/O

Z

PU/PD

20

VCC33_IO0

86

PA1

I/O

Z

PU/PD

20

VCC33_IO0

87

PA2

I/O

Z

PU/PD

20

VCC33_IO0

88

PA3

I/O

Z

PU/PD

20

VCC33_IO0

89

PA4

I/O

Z

PU/PD

20

VCC33_IO0

90

PA5

I/O

Z

PU/PD

20

VCC33_IO0

91

PA6

I/O

Z

PU/PD

20

VCC33_IO0

92

PA7

I/O

Z

PU/PD

20

VCC33_IO0

93

PA8

I/O

Z

PU/PD

20

VCC33_IO0

94

PA9

I/O

Z

PU/PD

20

VCC33_IO0

95

PA10

I/O

Z

PU/PD

20

VCC33_IO0

96

PA11

I/O

Z

PU/PD

20

VCC33_IO0

GPIO B

37

PB0

I/O

Z

PU/PD

20

VCC33_IO0

38

PB1

I/O

Z

PU/PD

20

VCC33_IO0

39

PB2

I/O

Z

PU/PD

20

VCC33_IO0

40

PB3

I/O

Z

PU/PD

20

VCC33_IO0

42

PB4

I/O

Z

PU/PD

20

VCC33_IO0

43

PB5

I/O

Z

PU/PD

20

VCC33_IO0

45

PB6

I/O

Z

PU/PD

20

VCC33_IO0

46

PB7

I/O

Z

PU/PD

20

VCC33_IO0

47

PB8

I/O

Z

PU/PD

20

VCC33_IO0

48

PB9

I/O

Z

PU/PD

20

VCC33_IO0

49

PB10

I/O

Z

PU/PD

20

VCC33_IO0

51

PB11

I/O

Z

PU/PD

20

VCC33_IO0

50

NC

I/O

Z

PU/PD

20

VCC33_IO0

56

NC

I/O

Z

PU/PD

20

VCC33_IO0

GPIO C

19

PC0

I/O

Z

PU/PD

20

VCC33_IO1

20

PC1

I/O

Z

PU/PD

20

VCC33_IO1

21

PC2

I/O

Z

PU/PD

20

VCC33_IO1

22

PC3

I/O

Z

PU/PD

20

VCC33_IO1

23

PC4

I/O

Z

PU/PD

20

VCC33_IO1

24

PC5

I/O

Z

PU/PD

20

VCC33_IO1

25

PC6

I/O

Z

PU/PD

20

VCC33_IO1

26

PC7

I/O

Z

PU/PD

20

VCC33_IO1

GPIO D

18

PD0

I/O

Z

PU/PD

20

VCC33_IO1

17

PD1

I/O

Z

PU/PD

20

VCC33_IO1

16

PD2

I/O

Z

PU/PD

20

VCC33_IO1

15

PD3

I/O

Z

PU/PD

20

VCC33_IO1

14

PD4

I/O

Z

PU/PD

20

VCC33_IO1

13

PD5

I/O

Z

PU/PD

20

VCC33_IO1

12

PD6

I/O

Z

PU/PD

20

VCC33_IO1

11

PD7

I/O

Z

PU/PD

20

VCC33_IO1

10

PD8

I/O

Z

PU/PD

20

VCC33_IO1

9

PD9

I/O

Z

PU/PD

20

VCC33_IO1

8

PD10

I/O

Z

PU/PD

20

VCC33_IO1

7

PD11

I/O

Z

PU/PD

20

VCC33_IO1

6

PD12

I/O

Z

PU/PD

20

VCC33_IO1

5

PD13

I/O

Z

PU/PD

20

VCC33_IO1

4

PD14

I/O

Z

PU/PD

20

VCC33_IO1

3

PD15

I/O

Z

PU/PD

20

VCC33_IO1

2

PD16

I/O

Z

PU/PD

20

VCC33_IO1

1

PD17

I/O

Z

PU/PD

20

VCC33_IO1

127

PD18

I/O

Z

PU/PD

20

VCC33_IO1

126

PD19

I/O

Z

PU/PD

20

VCC33_IO1

125

PD20

I/O

Z

PU/PD

20

VCC33_IO1

124

PD21

I/O

Z

PU/PD

20

VCC33_IO1

123

PD22

I/O

Z

PU/PD

20

VCC33_IO1

122

PD23

I/O

Z

PU/PD

20

VCC33_IO1

121

PD24

I/O

Z

PU/PD

20

VCC33_IO1

120

PD25

I/O

Z

PU/PD

20

VCC33_IO1

119

PD26

I/O

Z

PU/PD

20

VCC33_IO1

118

PD27

I/O

Z

PU/PD

20

VCC33_IO1

GPIO E

52

PE0

I/O

Z

PU/PD

20

VCC33_IO0

53

PE1

I/O

Z

PU/PD

20

VCC33_IO0

54

PE2

I/O

Z

PU/PD

20

VCC33_IO0

55

PE3

I/O

Z

PU/PD

20

VCC33_IO0

58

PE4

I/O

Z

PU/PD

20

VCC33_IO0

59

PE5

I/O

Z

PU/PD

20

VCC33_IO0

60

PE6

I/O

Z

PU/PD

20

VCC33_IO0

61

PE7

I/O

Z

PU/PD

20

VCC33_IO0

62

PE8

I/O

Z

PU/PD

20

VCC33_IO0

63

PE9

I/O

Z

PU/PD

20

VCC33_IO0

64

PE10

I/O

Z

PU/PD

20

VCC33_IO0

65

PE11

I/O

Z

PU/PD

20

VCC33_IO0

66

PE12

I/O

Z

PU/PD

20

VCC33_IO0

67

PE13

I/O

Z

PU/PD

20

VCC33_IO0

68

PE14

I/O

Z

PU/PD

20

VCC33_IO0

69

PE15

I/O

Z

PU/PD

20

VCC33_IO0

70

PE16

I/O

Z

PU/PD

20

VCC33_IO0

71

PE17

I/O

Z

PU/PD

20

VCC33_IO0

72

PE18

I/O

Z

PU/PD

20

VCC33_IO0

73

PE19

I/O

Z

PU/PD

20

VCC33_IO0

GPIO F

101

PF0

I/O

Z

PU/PD

20

VCC33_IO1

102

PF1

I/O

Z

PU/PD

20

VCC33_IO1

103

PF2

I/O

Z

PU/PD

20

VCC33_IO1

104

PF3

I/O

Z

PU/PD

20

VCC33_IO1

105

PF4

I/O

Z

PU/PD

20

VCC33_IO1

106

PF5

I/O

Z

PU/PD

20

VCC33_IO1

107

PF6

I/O

Z

PU/PD

20

VCC33_IO1

108

PF7

I/O

Z

PU/PD

20

VCC33_IO1

109

PF8

I/O

Z

PU/PD

20

VCC33_IO1

110

PF9

I/O

Z

PU/PD

20

VCC33_IO1

111

PF10

I/O

Z

PU/PD

20

VCC33_IO1

112

PF11

I/O

Z

PU/PD

20

VCC33_IO1

113

PF12

I/O

Z

PU/PD

20

VCC33_IO1

115

PF13

I/O

Z

PU/PD

20

VCC33_IO1

116

PF14

I/O

Z

PU/PD

20

VCC33_IO1

117

PF15

I/O

Z

PU/PD

20

VCC33_IO1

RTC

97

RTC_IO

OD

-

-

-

-

98

RTC_VCOIN

P

-

-

-

-

99

RTC_XO

O

-

-

-

-

100

RTC_XI

I

-

-

-

-

PLL

76

RESET

I

-

-

-

-

77

PLL_XO

O

-

-

-

-

78

PLL_XI

I

-

-

-

-

USB

79

USB0_DM

A

-

-

-

-

80

USB0_DP

A

81

USB1_DM

A

-

-

-

-

82

USB1_DP

A

-

-

-

-

Power

41,57,83

VCC33_IO0

P

-

-

-

-

27,114

VCC33_IO1

P

-

-

-

-

84

VCC30_ANA

P

-

-

-

-

29

LDO25

P

-

-

-

-

28

LDO1X

P

-

-

-

-

30,32,33,35,36

VCC_DRAM

P

-

-

-

-

31,34,44,74,75,128

VDD11_SYS

P

-

-

-

-

129

GND

P

-

-

-

-

5.3. 引脚功能复用¶

5.3.1. D21x 功能复用¶

引脚 |

功能2 |

功能3 |

功能4 |

功能5 |

功能6 |

功能7 |

功能8 |

|---|---|---|---|---|---|---|---|

PA0 |

GPADC0 |

PSADC0 |

I2C0_SCL |

UART0_TX |

AMIC_IN |

IR_TX |

|

PA1 |

GPADC1 |

PSADC1 |

I2C0_SDA |

UART0_RX |

AMIC_BIAS |

IR_RX |

|

PA2 |

GPADC2 |

PSADC2 |

UART0_RTS |

||||

PA3 |

GPADC3 |

PSADC3 |

UART0_CTS |

||||

PA4 |

GPADC4 |

PSADC4 |

UART1_TX |

||||

PA5 |

GPADC5 |

PSADC5 |

UART1_RX |

||||

PA6 |

GPADC6 |

PSADC6 |

I2C1_SCL |

UART1_RTS |

|||

PA7 |

GPADC7 |

PSADC7 |

I2C1_SDA |

UART1_CTS |

|||

PA8 |

RTP_XP |

PSADC8 |

I2C2_SCL |

UART2_TX |

JTAG_DO |

||

PA9 |

RTP_YP |

PSADC9 |

I2C2_SDA |

UART2_RX |

JTAG_DI |

||

PA10 |

RTP_XN |

PSADC10 |

I2C3_SCL |

UART2_RTS |

JTAG_MS |

||

PA11 |

RTP_YN |

PSADC11 |

I2C3_SDA |

UART2_CTS |

JTAG_CK |

||

PB0 |

SDC0_CMD |

SPI0_HOLD |

I2C1_SCL |

UART7_TX |

|||

PB1 |

SDC0_CLK |

SPI0_WP |

I2C1_SDA |

UART7_RX |

|||

PB2 |

SDC0_D3 |

SPI0_CS |

|||||

PB3 |

SDC0_D0 |

SPI0_MISO |

|||||

PB4 |

SDC0_D1 |

SPI0_MOSI |

|||||

PB5 |

SDC0_D2 |

SPI0_CLK |

|||||

PB6 |

SDC0_D4 |

SPI1_HOLD |

I2C2_SCL |

UART4_TX |

CLK_OUT2 |

CLK_OUT3 |

|

PB7 |

SDC0_D5 |

SPI1_WP |

I2C2_SDA |

UART4_RX |

|||

PB8 |

SDC0_D6 |

SPI1_CS |

UART4_RTS |

UART5_TX |

IR_RX |

||

PB9 |

SDC0_D7 |

SPI1_MISO |

UART6_RTS |

UART5_RX |

IR_TX |

||

PB10 |

SDC0_DS |

SPI1_MOSI |

UART6_TX |

||||

PB11 |

SDC0_RST |

SPI1_CLK |

UART6_RX |

||||

PC0 |

SDC1_D1 |

LCD_D5 |

SPI2_CLK |

UART1_TX |

JTAG_MS |

PWM0_A |

|

PC1 |

SDC1_D0 |

LCD_D4 |

SPI2_CS |

UART1_RX |

JTAG_DI |

PWM0_B |

|

PC2 |

SDC1_CLK |

LCD_D3 |

SPI2_MOSI |

UART1_RTS |

UART0_TX |

PWM1_A |

|

PC3 |

SDC1_CMD |

LCD_D2 |

SPI2_MISO |

UART2_TX |

JTAG_DO |

PWM1_B |

|

PC4 |

SDC1_D3 |

LCD_D1 |

UART2_RX |

UART0_RX |

PWM2_A |

||

PC5 |

SDC1_D2 |

LCD_D0 |

UART2_RTS |

UART3_TX |

JTAG_CK |

PWM2_B |

|

PC6 |

SDC1_DET |

CLK_OUT0 |

DE_TE |

UART3_RX |

PWM3_A |

||

PC7 |

UART3_RTS |

PWM3_B |

|||||

PD0 |

LCD_D0 |

SPI2_CLK |

PBUS_AD0 |

PWM0_A |

|||

PD1 |

LCD_D1 |

SPI2_CS |

PBUS_AD1 |

PWM0_B |

|||

PD2 |

LCD_D2 |

SPI2_MOSI |

DE_TE |

PBUS_AD2 |

PWM1_A |

||

PD3 |

LCD_D3 |

SPI3_CLK |

PBUS_AD3 |

PWM1_B |

|||

PD4 |

LCD_D4 |

SPI3_CS |

PBUS_AD4 |

PWM2_A |

|||

PD5 |

LCD_D5 |

SPI3_MOSI |

PBUS_AD5 |

PWM2_B |

|||

PD6 |

LCD_D6 |

SPI3_MISO |

I2C0_SCL |

UART1_TX |

PBUS_AD6 |

||

PD7 |

LCD_D7 |

SPI2_MISO |

I2C0_SDA |

UART1_RX |

PBUS_AD7 |

||

PD8 |

LCD_D8 |

LVDS1_D0N |

SPI1_HOLD |

UART2_TX |

PBUS_AD8 |

EPWM0_A |

|

PD9 |

LCD_D9 |

LVDS1_D0P |

SPI1_WP |

UART2_RX |

PBUS_AD9 |

EPWM0_B |

|

PD10 |

LCD_D10 |

LVDS1_D1N |

SPI1_CS |

UART3_TX |

PBUS_AD10 |

EPWM1_A |

|

PD11 |

LCD_D11 |

LVDS1_D1P |

SPI1_MISO |

UART3_RX |

PBUS_AD11 |

EPWM1_B |

|

PD12 |

LCD_D12 |

LVDS1_D2N |

SPI1_MOSI |

UART4_TX |

PBUS_AD12 |

EPWM2_A |

|

PD13 |

LCD_D13 |

LVDS1_D2P |

SPI1_CLK |

UART4_RX |

PBUS_AD13 |

EPWM2_B |

|

PD14 |

LCD_D14 |

LVDS1_CKN |

SPI3_CLK |

CAP0 |

PBUS_AD14 |

QEP0_H0 |

|

PD15 |

LCD_D15 |

LVDS1_CKP |

SPI3_CS |

CAP1 |

PBUS_AD15 |

QEP0_H1 |

|

PD16 |

LCD_D16 |

LVDS1_D3N |

SPI3_MOSI |

CAP2 |

PBUS_CLK |

QEP0_H2 |

|

PD17 |

LCD_D17 |

LVDS1_D3P |

SPI3_MISO |

PBUS_NCS |

QEP0_A |

||

PD18 |

LCD_D18 |

LVDS0_D0N |

DSI_D0N |

I2C1_SCL |

PBUS_NADV |

QEP0_B |

|

PD19 |

LCD_D19 |

LVDS0_D0P |

DSI_D0P |

I2C1_SDA |

PBUS_NWE |

QEP0_I |

|

PD20 |

LCD_D20 |

LVDS0_D1N |

DSI_D1N |

UART7_TX |

PBUS_NOE |

QEP0_S |

|

PD21 |

LCD_D21 |

LVDS0_D1P |

DSI_D1P |

UART7_RX |

CLK_OUT0 |

||

PD22 |

LCD_D22 |

LVDS0_D2N |

DSI_CKN |

I2C3_SCL |

UART6_TX |

||

PD23 |

LCD_D23 |

LVDS0_D2P |

DSI_CKP |

I2C3_SDA |

UART6_RX |

||

PD24 |

LCD_DCLK |

LVDS0_CKN |

DSI_D2N |

UART5_TX |

SPI1_CLK |

||

PD25 |

LCD_HS |

LVDS0_CKP |

DSI_D2P |

UART5_RX |

SPI1_CS |

||

PD26 |

LCD_VS |

LVDS0_D3N |

DSI_D3N |

PWM3_A |

SPI1_MOSI |

||

PD27 |

LCD_DE |

LVDS0_D3P |

DSI_D3P |

PWM3_B |

SPI1_MISO |

RTC_32K |

|

PE0 |

DVP_D0 |

I2C0_SCL |

GMAC0_RXD1 |

EPWM3_A |

PWM0_A |

||

PE1 |

DVP_D1 |

I2C0_SDA |

GMAC0_RXD0 |

EPWM3_B |

PWM0_B |

||

PE2 |

DVP_D2 |

CAN0_TX |

UART4_TX |

GMAC0_RXCTL |

EPWM4_A |

PWM1_A |

|

PE3 |

DVP_D3 |

CAN0_RX |

UART4_RX |

GMAC0_CLKIN |

EPWM4_B |

PWM1_B |

|

PE4 |

DVP_D4 |

CAN1_TX |

UART5_TX |

GMAC0_TXD1 |

EPWM5_A |

PWM2_A |

|

PE5 |

DVP_D5 |

CAN1_RX |

UART5_RX |

GMAC0_TXD0 |

EPWM5_B |

PWM2_B |

|

PE6 |

DSPK0 |

DVP_D6 |

UART5_RTS |

UART6_TX |

GMAC0_TXCK |

QEP1_H0 |

CAP0 |

PE7 |

DSPK1 |

DVP_D7 |

UART7_RTS |

UART6_RX |

GMAC0_TXCTL |

QEP1_H1 |

CAP1 |

PE8 |

I2S0_MCLK |

DVP_CK |

UART6_RTS |

UART7_TX |

GMAC0_MDC |

QEP1_H2 |

CAP2 |

PE9 |

I2S0_BCLK |

DVP_HS |

UART6_CTS |

UART7_RX |

GMAC0_MDIO |

QEP1_A |

|

PE10 |

I2S0_LRCK |

DVP_VS |

DSPK0 |

CLK_OUT2 |

QEP1_B |

||

PE11 |

I2S0_DOUT |

I2S0_DIN |

DSPK1 |

CLK_OUT1 |

GMAC0_RXD3 |

QEP1_I |

|

PE12 |

I2S0_DIN |

SPI3_CLK |

DMIC_CLK |

I2C2_SCL |

GMAC0_RXD2 |

QEP1_S |

|

PE13 |

SPI3_CS |

DMIC_D0 |

I2C2_SDA |

GMAC0_RXCK |

CAP0 |

||

PE14 |

SPI3_MOSI |

UART3_TX |

GMAC0_TXD3 |

CAP1 |

|||

PE15 |

SPI3_MISO |

UART3_RX |

GMAC0_TXD2 |

CAP2 |

|||

PE16 |

SPI0_CLK |

CAN0_TX |

I2C3_SCL |

GMAC0_TRIG |

|||

PE17 |

SPI0_CS |

CAN0_RX |

I2C3_SDA |

GMAC0_PPSO |

|||

PE18 |

SPI0_MOSI |

CAN1_TX |

PWM3_A |

GMAC1_TRIG |

|||

PE19 |

SPI0_MISO |

CAN1_RX |

PWM3_B |

GMAC1_PPSO |

|||

PF0 |

SDC2_D1 |

SPI2_CLK |

UART5_TX |

GMAC1_RXD1 |

PBUS_AD0 |

||

PF1 |

SDC2_D0 |

SPI2_CS |

UART5_RX |

GMAC1_RXD0 |

PBUS_AD1 |

||

PF2 |

SDC2_CLK |

SPI2_MOSI |

UART5_RTS |

GMAC1_RXCTL |

PBUS_AD2 |

||

PF3 |

SDC2_CMD |

SPI2_MISO |

UART5_CTS |

GMAC1_CLKIN |

PBUS_AD3 |

||

PF4 |

SDC2_D3 |

UART6_TX |

GMAC1_TXD1 |

PBUS_AD4 |

|||

PF5 |

SDC2_D2 |

UART6_RX |

GMAC1_TXD0 |

PBUS_AD5 |

|||

PF6 |

UART7_TX |

GMAC1_TXCK |

PBUS_AD6 |

||||

PF7 |

UART7_RX |

GMAC1_TXCTL |

PBUS_AD7 |

||||

PF8 |

UART7_RTS |

GMAC1_MDC |

PBUS_AD8 |

||||

PF9 |

UART7_CTS |

GMAC1_MDIO |

PBUS_AD9 |

||||

PF10 |

I2S1_MCLK |

I2S1_DIN |

UART3_CTS |

CLK_OUT3 |

PBUS_AD10 |

||

PF11 |

I2S1_BCLK |

PBUS_AD11 |

UART3_TX |

GMAC1_RXD3 |

PBUS_CLK |

||

PF12 |

I2S1_LRCK |

UART4_RTS |

UART3_RX |

GMAC1_RXD2 |

PBUS_NCS |

||

PF13 |

I2S1_DOUT |

I2S1_DIN |

UART4_CTS |

UART3_RTS |

GMAC1_RXCK |

PBUS_NADV |

|

PF14 |

I2S1_DIN |

DSPK0 |

DMIC_D0 |

UART4_TX |

GMAC1_TXD3 |

PBUS_NWE |

|

PF15 |

DE_TE |

DSPK1 |

DMIC_CLK |

UART4_RX |

GMAC1_TXD2 |

PBUS_NOE |

|

PU0 |

USB0_DM |

UART0_RX |

UART1_RX |

||||

PU1 |

USB0_DP |

UART0_TX |

UART1_TX |

||||

PU2 |

USB1_DM |

UART0_RX |

UART2_RX |

||||

PU3 |

USB1_DP |

UART0_TX |

UART2_TX |

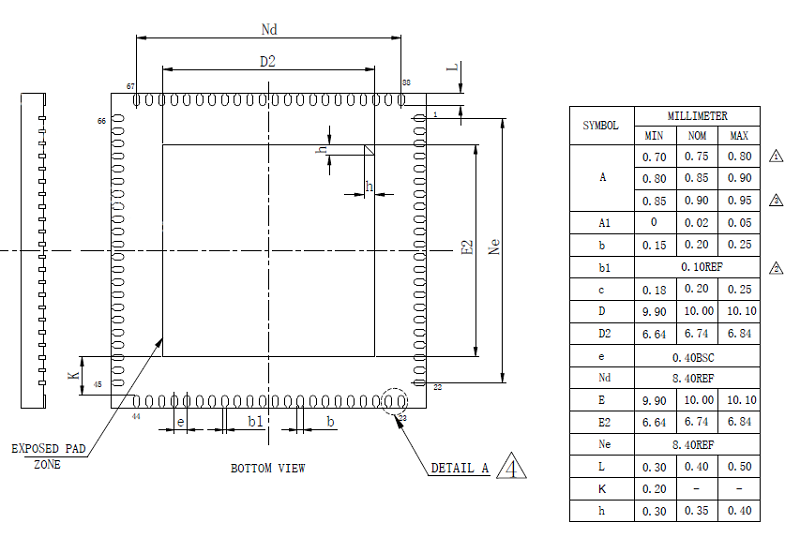

5.3.2. D211BB/D211BC QFN88 封装引脚说明¶

引脚 |

定义 |

类型 |

功能 |

备注说明 |

|---|---|---|---|---|

RTC |

||||

1 |

RTC_IO |

OD |

RTC唤醒

32K时钟输出

|

OD输出,外部需上拉电阻,上拉电压不能超过5V |

2 |

RTC_VCOIN |

POWER |

- |

不考虑掉电保持可悬空,内部有二极管从3.3V取电 |

3 |

RTC_XO |

OUTPUT |

- |

接32.768kHz无源晶振,若不使用RTC功能可悬空 |

4 |

RTC_XI |

INPUT |

- |

接32.768kHz无源晶振,若不使用RTC功能可悬空 |

SYS |

||||

75 |

RESETN |

INPUT |

系统复位 |

内置约30Kohm上拉电阻和去抖滤波,不使用可

直接悬空,若外挂电容建议不超过4.7uF

|

76 |

PLL_XO |

OUTPUT |

- |

接24MHz无源晶振 |

77 |

PLL_XI |

INPUT |

- |

接24MHz无源晶振 |

Power |

||||

58,80 |

VCC33_IO0 |

POWER |

CPU IO电压 |

3.3V供电 |

7,40 |

VCC33_IO1 |

POWER |

CPU IO电压 |

3.3V供电 |

81 |

VCC30_ANA |

POWER |

内置LDO输出 |

部模拟模块使用,外部接1uf旁路电容 |

42 |

LDO25 |

POWER |

内置LDO输出 |

内部模块使用,外部接1uf旁路电容 |

41 |

LDO1x |

POWER |

内置LDO输出 |

可配置,外部接1uf电容,若使用需做好芯片散热 |

43,45,46 |

VCC_DRAM |

POWER |

DRAM电压 |

DDR2 1.8V供电;DDR3 1.5V供电 |

20,44,53,73,74 |

VDD11_SYS |

POWER |

CPU Core电压 |

1.2V供电@600Mhz,1.1V供电@504Mhz |

89 |

GND |

POWER |

- |

GND铜皮全连接,需多加过孔散热 |

引脚 |

功能1 |

功能2 |

功能3 |

功能4 |

功能5 |

功能6 |

功能7 |

功能8 |

|---|---|---|---|---|---|---|---|---|

GPIO A |

||||||||

82 |

PA0 |

GPADC0 |

PSADC0 |

I2C0_SCL |

UART0_TX |

AMIC_IN |

IR_TX |

|

83 |

PA1 |

GPADC1 |

PSADC1 |

I2C0_SDA |

UART0_RX |

AMIC_BIAS |

IR_RX |

|

84 |

PA7 |

GPADC7 |

PSADC7 |

I2C1_SDA |

UART1_CTS |

|||

85 |

PA8 |

RTP_XP |

PSADC8 |

I2C2_SCL |

UART2_TX |

JTAG_DO |

||

86 |

PA9 |

RTP_YP |

PSADC9 |

I2C2_SDA |

UART2_RX |

JTAG_DI |

||

87 |

PA10 |

RTP_XN |

PSADC10 |

I2C3_SCL |

UART2_RTS |

JTAG_MS |

||

88 |

PA11 |

RTP_YN |

PSADC11 |

I2C3_SDA |

UART2_CTS |

JTAG_CK |

||

GPIO B |

||||||||

47 |

PB0 |

SDC0_CMD |

SPI0_HOLD |

I2C1_SCL |

UART7_TX |

|||

48 |

PB1 |

SDC0_CLK |

SPI0_WP |

I2C1_SDA |

UART7_RX |

|||

49 |

PB2 |

SDC0_D3 |

SPI0_CS |

|||||

50 |

PB3 |

SDC0_D0 |

SPI0_MISO |

|||||

51 |

PB4 |

SDC0_D1 |

SPI0_MOSI |

|||||

52 |

PB5 |

SDC0_D2 |

SPI0_CLK |

|||||

GPIO C |

||||||||

33 |

PC0 |

SDC1_D1 |

LCD_D5 |

SPI2_CLK |

UART1_TX |

JTAG_MS |

PWM0_A |

|

34 |

PC1 |

SDC1_D0 |

LCD_D4 |

SPI2_CS |

UART1_RX |

JTAG_DI |

PWM0_B |

|

35 |

PC2 |

SDC1_CLK |

LCD_D3 |

SPI2_MOSI |

UART1_RTS |

UART0_TX |

PWM1_A |

|

36 |

PC3 |

SDC1_CMD |

LCD_D2 |

SPI2_MISO |

UART2_TX |

JTAG_DO |

PWM1_B |

|

37 |

PC4 |

SDC1_D3 |

LCD_D1 |

UART2_RX |

UART0_RX |

PWM2_A |

||

38 |

PC5 |

SDC1_D2 |

LCD_D0 |

UART2_RTS |

UART3_TX |

JTAG_CK |

PWM2_B |

|

39 |

PC6 |

SDC1_DET |

CLK_OUT0 |

DE_TE |

UART3_RX |

PWM3_A |

||

GPIO D |

||||||||

32 |

PD6 |

LCD_D6 |

SPI3_MISO |

I2C0_SCL |

UART1_TX |

|||

31 |

PD7 |

LCD_D7 |

SPI2_MISO |

I2C0_SDA |

UART1_RX |

|||

30 |

PD8 |

LCD_D8 |

LVDS1_D0N |

SPI1_HOLD |

UART2_TX |

EPWM0_A |

||

29 |

PD9 |

LCD_D9 |

LVDS1_D0P |

SPI1_WP |

UART2_RX |

EPWM0_B |

||

28 |

PD10 |

LCD_D10 |

LVDS1_D1N |

SPI1_CS |

UART3_TX |

EPWM1_A |

||

27 |

PD11 |

LCD_D11 |

LVDS1_D1P |

SPI1_MISO |

UART3_RX |

EPWM1_B |

||

26 |

PD12 |

LCD_D12 |

LVDS1_D2N |

SPI1_MOSI |

UART4_TX |

EPWM2_A |

||

25 |

PD13 |

LCD_D13 |

LVDS1_D2P |

SPI1_CLK |

UART4_RX |

EPWM2_B |

||

24 |

PD14 |

LCD_D14 |

LVDS1_CKN |

SPI3_CLK |

CAP0 |

QEP0_H0 |

||

23 |

PD15 |

LCD_D15 |

LVDS1_CKP |

SPI3_CS |

CAP1 |

QEP0_H1 |

||

22 |

PD16 |

LCD_D16 |

LVDS1_D3N |

SPI3_MOSI |

CAP2 |

QEP0_H2 |

||

21 |

PD17 |

LCD_D17 |

LVDS1_D3P |

SPI3_MISO |

QEP0_A |

|||

19 |

PD18 |

LCD_D18 |

LVDS0_D0N |

DSI_D0N |

I2C1_SCL |

QEP0_B |

||

18 |

PD19 |

LCD_D19 |

LVDS0_D0P |

DSI_D0P |

I2C1_SDA |

QEP0_I |

||

17 |

PD20 |

LCD_D20 |

LVDS0_D1N |

DSI_D1N |

UART7_TX |

QEP0_S |

||

16 |

PD21 |

LCD_D21 |

LVDS0_D1P |

DSI_D1P |

UART7_RX |

CLK_OUT0 |

||

15 |

PD22 |

LCD_D22 |

LVDS0_D2N |

DSI_CKN |

I2C3_SCL |

UART6_TX |

||

14 |

PD23 |

LCD_D23 |

LVDS0_D2P |

DSI_CKP |

I2C3_SDA |

UART6_RX |

||

13 |

PD24 |

LCD_DCLK |

LVDS0_CKN |

DSI_D2N |

UART5_TX |

SPI1_CLK |

||

12 |

PD25 |

LCD_HS |

LVDS0_CKP |

DSI_D2P |

UART5_RX |

SPI1_CS |

||

11 |

PD26 |

LCD_VS |

LVDS0_D3N |

DSI_D3N |

PWM3_A |

SPI1_MOSI |

||

10 |

PD27 |

LCD_DE |

LVDS0_D3P |

DSI_D3P |

PWM3_B |

SPI1_MISO |

RTC_32K |

|

GPIO E |

||||||||

54 |

PE0 |

DVP_D0 |

I2C0_SCL |

EMAC0_RXD1 |

EPWM3_A |

PWM0_A |

||

55 |

PE1 |

DVP_D1 |

I2C0_SDA |

EMAC0_RXD0 |

EPWM3_B |

PWM0_B |

||

56 |

PE2 |

DVP_D2 |

CAN0_TX |

UART4_TX |

EMAC0_CRS_DV |

EPWM4_A |

PWM1_A |

|

57 |

PE3 |

DVP_D3 |

CAN0_RX |

UART4_RX |

EMAC0_REFCLK |

EPWM4_B |

PWM1_B |

|

59 |

PE4 |

DVP_D4 |

CAN1_TX |

UART5_TX |

EMAC0_TXD1 |

EPWM5_A |

PWM2_A |

|

60 |

PE5 |

DVP_D5 |

CAN1_RX |

UART5_RX |

EMAC0_TXD0 |

EPWM5_B |

PWM2_B |

|

61 |

PE6 |

DSPK0 |

DVP_D6 |

UART5_RTS |

UART6_TX |

EMAC0_TXC |

QEP1_H0 |

CAP0 |

62 |

PE7 |

DSPK1 |

DVP_D7 |

UART7_RTS |

UART6_RX |

EMAC0_TXEN |

QEP1_H1 |

CAP1 |

63 |

PE8 |

I2S0_MCLK |

DVP_CK |

UART6_RTS |

UART7_TX |

EMAC0_MDC |

QEP1_H2 |

CAP2 |

64 |

PE9 |

I2S0_BCLK |

DVP_HS |

UART6_CTS |

UART7_RX |

EMAC0_MDIO |

QEP1_A |

|

65 |

PE10 |

I2S0_LRCK |

DVP_VS |

DSPK0 |

CLK_OUT2 |

QEP1_B |

||

66 |

PE11 |

I2S0_DOUT |

I2S0_DIN |

DSPK1 |

CLK_OUT1 |

QEP1_I |

||

67 |

PE14 |

SPI3_MOSI |

UART3_TX |

CAP1 |

||||

68 |

PE15 |

SPI3_MISO |

UART3_RX |

CAP2 |

||||

69 |

PE16 |

SPI0_CLK |

CAN0_TX |

I2C3_SCL |

||||

70 |

PE17 |

SPI0_CS |

CAN0_RX |

I2C3_SDA |

||||

71 |

PE18 |

SPI0_MOSI |

CAN1_TX |

PWM3_A |

||||

72 |

PE19 |

SPI0_MISO |

CAN1_RX |

PWM3_B |

||||

GPIO F |

||||||||

5 |

PF0 |

SDC2_D1 |

SPI2_CLK |

UART5_TX |

||||

6 |

PF1 |

SDC2_D0 |

SPI2_CS |

UART5_RX |

||||

8 |

PF14 |

I2S1_DIN |

DSPK0 |

DMIC_D0 |

UART4_TX |

|||

9 |

PF15 |

DE_TE |

DSPK1 |

DMIC_CLK |

UART4_RX |

|||

USB |

||||||||

78 |

PU0 |

USB0_DM |

UART0_RX |

UART1_RX |

||||

79 |

PU1 |

USB0_DP |

UART0_TX |

UART1_TX |

||||

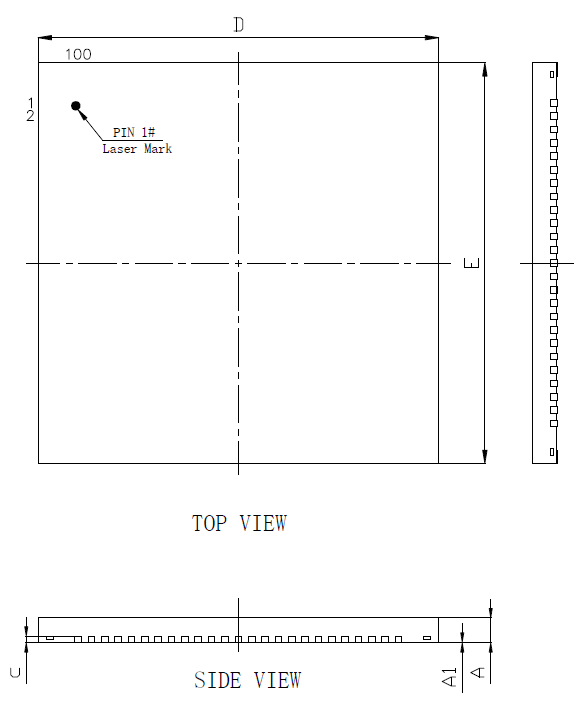

5.3.3. D211DB/D211DC QFN100 封装引脚说明¶

引脚 |

定义 |

类型 |

功能 |

备注说明 |

|---|---|---|---|---|

RTC |

||||

74 |

RTC_IO |

OD |

RTC唤醒

32K时钟输出

|

OD输出,外部需上拉电阻,上拉电压不能超过5V |

75 |

RTC_VCOIN |

POWER |

- |

不考虑掉电保持可悬空,内部有二极管从3.3V取电 |

76 |

RTC_XO |

OUTPUT |

- |

接32.768kHz无源晶振,若不使用RTC功能可悬空 |

77 |

RTC_XI |

INPUT |

- |

接32.768kHz无源晶振,若不使用RTC功能可悬空 |

SYS |

||||

58 |

RESETN |

INPUT |

系统复位 |

内置约30Kohm上拉电阻和去抖滤波,不使用可

直接悬空,若外挂电容建议不超过4.7uF

|

59 |

PLL_XO |

OUTPUT |

- |

接24MHz无源晶振 |

60 |

PLL_XI |

INPUT |

- |

接24MHz无源晶振 |

Power |

||||

41,65 |

VCC33_IO0 |

POWER |

CPU IO电压 |

3.3V供电 |

21,88 |

VCC33_IO1 |

POWER |

CPU IO电压 |

3.3V供电 |

66 |

VCC30_ANA |

POWER |

内置LDO输出 |

部模拟模块使用,外部接1uf旁路电容 |

23 |

LDO25 |

POWER |

内置LDO输出 |

内部模块使用,外部接1uf旁路电容 |

22 |

LDO1x |

POWER |

内置LDO输出 |

可配置,外部接1uf电容,若使用需做好芯片散热 |

24,26,27,29 |

VCC_DRAM |

POWER |

DRAM电压 |

DDR2 1.8V供电;DDR3 1.5V供电 |

1,25,28,36,56,57 |

VDD11_SYS |

POWER |

CPU Core电压 |

1.2V供电@600Mhz,1.1V供电@504Mhz |

101 |

GND |

POWER |

- |

GND铜皮全连接,需多加过孔散热 |

引脚 |

功能1 |

功能2 |

功能3 |

功能4 |

功能5 |

功能6 |

功能7 |

功能8 |

|---|---|---|---|---|---|---|---|---|

GPIO A |

||||||||

67 |

PA0 |

GPADC0 |

PSADC0 |

I2C0_SCL |

UART0_TX |

AMIC_IN |

IR_TX |

|

68 |

PA1 |

GPADC1 |

PSADC1 |

I2C0_SDA |

UART0_RX |

AMIC_BIAS |

IR_RX |

|

69 |

PA7 |

GPADC7 |

PSADC7 |

I2C1_SDA |

UART1_CTS |

|||

70 |

PA8 |

RTP_XP |

PSADC8 |

I2C2_SCL |

UART2_TX |

JTAG_DO |

||

71 |

PA9 |

RTP_YP |

PSADC9 |

I2C2_SDA |

UART2_RX |

JTAG_DI |

||

72 |

PA10 |

RTP_XN |

PSADC10 |

I2C3_SCL |

UART2_RTS |

JTAG_MS |

||

73 |

PA11 |

RTP_YN |

PSADC11 |

I2C3_SDA |

UART2_CTS |

JTAG_CK |

||

GPIO B |

||||||||

30 |

PB0 |

SDC0_CMD |

SPI0_HOLD |

I2C1_SCL |

UART7_TX |

|||

31 |

PB1 |

SDC0_CLK |

SPI0_WP |

I2C1_SDA |

UART7_RX |

|||

32 |

PB2 |

SDC0_D3 |

SPI0_CS |

|||||

33 |

PB3 |

SDC0_D0 |

SPI0_MISO |

|||||

34 |

PB4 |

SDC0_D1 |

SPI0_MOSI |

|||||

35 |

PB5 |

SDC0_D2 |

SPI0_CLK |

|||||

GPIO C |

||||||||

14 |

PC0 |

SDC1_D1 |

LCD_D5 |

SPI2_CLK |

UART1_TX |

JTAG_MS |

PWM0_A |

|

15 |

PC1 |

SDC1_D0 |

LCD_D4 |

SPI2_CS |

UART1_RX |

JTAG_DI |

PWM0_B |

|

16 |

PC2 |

SDC1_CLK |

LCD_D3 |

SPI2_MOSI |

UART1_RTS |

UART0_TX |

PWM1_A |

|

17 |

PC3 |

SDC1_CMD |

LCD_D2 |

SPI2_MISO |

UART2_TX |

JTAG_DO |

PWM1_B |

|

18 |

PC4 |

SDC1_D3 |

LCD_D1 |

UART2_RX |

UART0_RX |

PWM2_A |

||

19 |

PC5 |

SDC1_D2 |

LCD_D0 |

UART2_RTS |

UART3_TX |

JTAG_CK |

PWM2_B |

|

20 |

PC6 |

SDC1_DET |

CLK_OUT0 |

DE_TE |

UART3_RX |

PWM3_A |

||

GPIO D |

||||||||

13 |

PD6 |

LCD_D6 |

SPI3_MISO |

I2C0_SCL |

UART1_TX |

PBUS_AD6 |

||

12 |

PD7 |

LCD_D7 |

SPI2_MISO |

I2C0_SDA |

UART1_RX |

PBUS_AD7 |

||

11 |

PD8 |

LCD_D8 |

LVDS1_D0N |

SPI1_HOLD |

UART2_TX |

PBUS_AD8 |

EPWM0_A |

|

10 |

PD9 |

LCD_D9 |

LVDS1_D0P |

SPI1_WP |

UART2_RX |

PBUS_AD9 |

EPWM0_B |

|

9 |

PD10 |

LCD_D10 |

LVDS1_D1N |

SPI1_CS |

UART3_TX |

PBUS_AD10 |

EPWM1_A |

|

8 |

PD11 |

LCD_D11 |

LVDS1_D1P |

SPI1_MISO |

UART3_RX |

PBUS_AD11 |

EPWM1_B |

|

7 |

PD12 |

LCD_D12 |

LVDS1_D2N |

SPI1_MOSI |

UART4_TX |

PBUS_AD12 |

EPWM2_A |

|

6 |

PD13 |

LCD_D13 |

LVDS1_D2P |

SPI1_CLK |

UART4_RX |

PBUS_AD13 |

EPWM2_B |

|

5 |

PD14 |

LCD_D14 |

LVDS1_CKN |

SPI3_CLK |

CAP0 |

PBUS_AD14 |

QEP0_H0 |

|

4 |

PD15 |

LCD_D15 |

LVDS1_CKP |

SPI3_CS |

CAP1 |

PBUS_AD15 |

QEP0_H1 |

|

3 |

PD16 |

LCD_D16 |

LVDS1_D3N |

SPI3_MOSI |

CAP2 |

PBUS_CLK |

QEP0_H2 |

|

2 |

PD17 |

LCD_D17 |

LVDS1_D3P |

SPI3_MISO |

PBUS_NCS |

QEP0_A |

||

100 |

PD18 |

LCD_D18 |

LVDS0_D0N |

DSI_D0N |

I2C1_SCL |

PBUS_NADV |

QEP0_B |

|

99 |

PD19 |

LCD_D19 |

LVDS0_D0P |

DSI_D0P |

I2C1_SDA |

PBUS_NWE |

QEP0_I |

|

98 |

PD20 |

LCD_D20 |

LVDS0_D1N |

DSI_D1N |

UART7_TX |

PBUS_NOE |

QEP0_S |

|

97 |

PD21 |

LCD_D21 |

LVDS0_D1P |

DSI_D1P |

UART7_RX |

CLK_OUT0 |

||

96 |

PD22 |

LCD_D22 |

LVDS0_D2N |

DSI_CKN |

I2C3_SCL |

UART6_TX |

||

95 |

PD23 |

LCD_D23 |

LVDS0_D2P |

DSI_CKP |

I2C3_SDA |

UART6_RX |

||

94 |

PD24 |

LCD_DCLK |

LVDS0_CKN |

DSI_D2N |

UART5_TX |

SPI1_CLK |

||

93 |

PD25 |

LCD_HS |

LVDS0_CKP |

DSI_D2P |

UART5_RX |

SPI1_CS |

||

92 |

PD26 |

LCD_VS |

LVDS0_D3N |

DSI_D3N |

PWM3_A |

SPI1_MOSI |

||

91 |

PD27 |

LCD_DE |

LVDS0_D3P |

DSI_D3P |

PWM3_B |

SPI1_MISO |

RTC_32K |

|

GPIO E |

||||||||

37 |

PE0 |

DVP_D0 |

I2C0_SCL |

EMAC0_RXD1 |

EPWM3_A |

PWM0_A |

||

38 |

PE1 |

DVP_D1 |

I2C0_SDA |

EMAC0_RXD0 |

EPWM3_B |

PWM0_B |

||

39 |

PE2 |

DVP_D2 |

CAN0_TX |

UART4_TX |

EMAC0_CRS_DV |

EPWM4_A |

PWM1_A |

|

40 |

PE3 |

DVP_D3 |

CAN0_RX |

UART4_RX |

EMAC0_REFCLK |

EPWM4_B |

PWM1_B |

|

42 |

PE4 |

DVP_D4 |

CAN1_TX |

UART5_TX |

EMAC0_TXD1 |

EPWM5_A |

PWM2_A |

|

43 |

PE5 |

DVP_D5 |

CAN1_RX |

UART5_RX |

EMAC0_TXD0 |

EPWM5_B |

PWM2_B |

|

44 |

PE6 |

DSPK0 |

DVP_D6 |

UART5_RTS |

UART6_TX |

EMAC0_TXC |

QEP1_H0 |

CAP0 |

45 |

PE7 |

DSPK1 |

DVP_D7 |

UART7_RTS |

UART6_RX |

EMAC0_TXEN |

QEP1_H1 |

CAP1 |

46 |

PE8 |

I2S0_MCLK |

DVP_CK |

UART6_RTS |

UART7_TX |

EMAC0_MDC |

QEP1_H2 |

CAP2 |

47 |

PE9 |

I2S0_BCLK |

DVP_HS |

UART6_CTS |

UART7_RX |

EMAC0_MDIO |

QEP1_A |

|

48 |

PE10 |

I2S0_LRCK |

DVP_VS |

DSPK0 |

CLK_OUT2 |

QEP1_B |

||

49 |

PE11 |

I2S0_DOUT |

I2S0_DIN |

DSPK1 |

CLK_OUT1 |

QEP1_I |

||

50 |

PE14 |

SPI3_MOSI |

UART3_TX |

CAP1 |

||||

51 |

PE15 |

SPI3_MISO |

UART3_RX |

CAP2 |

||||

52 |

PE16 |

SPI0_CLK |

CAN0_TX |

I2C3_SCL |

||||

53 |

PE17 |

SPI0_CS |

CAN0_RX |

I2C3_SDA |

||||

54 |

PE18 |

SPI0_MOSI |

CAN1_TX |

PWM3_A |

||||

55 |

PE19 |

SPI0_MISO |

CAN1_RX |

PWM3_B |

||||

GPIO F |

||||||||

78 |

PF0 |

SDC2_D1 |

SPI2_CLK |

UART5_TX |

EMAC1_RXD1 |

PBUS_AD0 |

||

79 |

PF1 |

SDC2_D0 |

SPI2_CS |

UART5_RX |

EMAC1_RXD0 |

PBUS_AD1 |

||

80 |

PF2 |

SDC2_CLK |

SPI2_MOSI |

UART5_RTS |

EMAC1_CRS_DV |

PBUS_AD2 |

||

81 |

PF3 |

SDC2_CMD |

SPI2_MISO |

UART5_CTS |

EMAC1_REFCLK |

PBUS_AD3 |

||

82 |

PF4 |

SDC2_D3 |

UART6_TX |

EMAC1_TXD1 |

PBUS_AD4 |

|||

83 |

PF5 |

SDC2_D2 |

UART6_RX |

EMAC1_TXD0 |

PBUS_AD5 |

|||

84 |

PF6 |

UART7_TX |

EMAC1_TXC |

PBUS_AD6 |

||||

85 |

PF7 |

UART7_RX |

EMAC1_TXEN |

PBUS_AD7 |

||||

86 |

PF8 |

UART7_RTS |

EMAC1_MDC |

PBUS_AD8 |

||||

87 |

PF9 |

UART7_CTS |

EMAC1_MDIO |

PBUS_AD9 |

||||

89 |

PF14 |

I2S1_DIN |

DSPK0 |

DMIC_D0 |

UART4_TX |

PBUS_NWE |

||

90 |

PF15 |

DE_TE |

DSPK1 |

DMIC_CLK |

UART4_RX |

PBUS_NOE |

||

USB |

||||||||

61 |

PU0 |

USB0_DM |

UART0_RX |

UART1_RX |

||||

62 |

PU1 |

USB0_DP |

UART0_TX |

UART1_TX |

||||

63 |

PU2 |

USB1_DM |

UART0_RX |

UART2_RX |

||||

64 |

PU3 |

USB1_DP |

UART0_TX |

UART2_TX |

||||

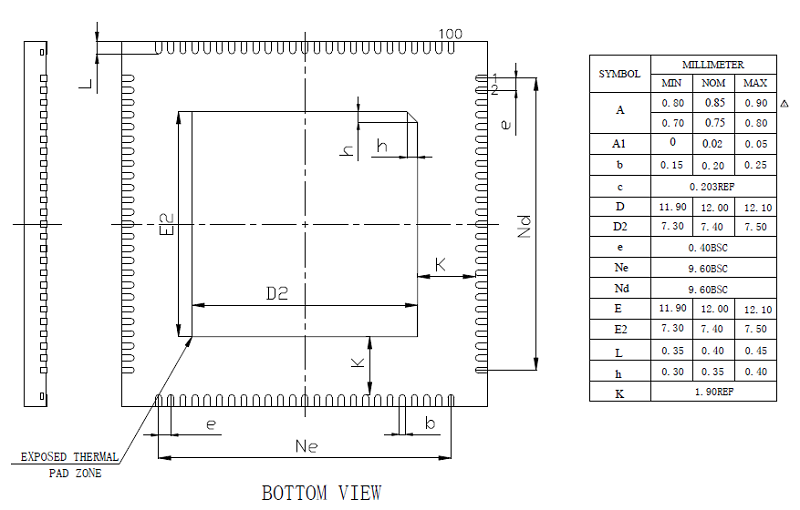

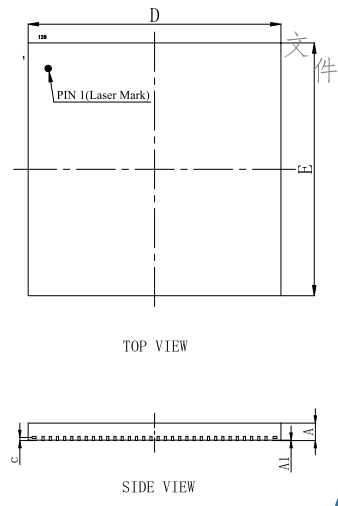

5.3.4. D213EC QFN128 封装引脚说明¶

引脚 |

定义 |

类型 |

功能 |

备注说明 |

|---|---|---|---|---|

RTC |

||||

97 |

RTC_IO |

OD |

RTC唤醒

32K时钟输出

|

OD输出,外部需上拉电阻,上拉电压不能超过5V |

98 |

RTC_VCOIN |

POWER |

- |

不考虑掉电保持可悬空,内部有二极管从3.3V取电 |

99 |

RTC_XO |

OUTPUT |

- |

接32.768kHz无源晶振,若不使用RTC功能可悬空 |

100 |

RTC_XI |

INPUT |

- |

接32.768kHz无源晶振,若不使用RTC功能可悬空 |

SYS |

||||

76 |

RESETN |

INPUT |

系统复位 |

内置约30Kohm上拉电阻和去抖滤波,不使用可

直接悬空,若外挂电容建议不超过4.7uF

|

77 |

PLL_XO |

OUTPUT |

- |

接24MHz无源晶振 |

78 |

PLL_XI |

INPUT |

- |

接24MHz无源晶振 |

Power |

||||

41,57,83 |

VCC33_IO0 |

POWER |

CPU IO电压 |

3.3V供电 |

27,114 |

VCC33_IO1 |

POWER |

CPU IO电压 |

3.3V供电 |

84 |

VCC30_ANA |

POWER |

内置LDO输出 |

部模拟模块使用,外部接1uf旁路电容 |

29 |

LDO25 |

POWER |

内置LDO输出 |

内部模块使用,外部接1uf旁路电容 |

28 |

LDO1x |

POWER |

内置LDO输出 |

可配置,外部接1uf电容,若使用需做好芯片散热 |

30,32,33,35,36 |

VCC_DRAM |

POWER |

DRAM电压 |

DDR2 1.8V供电;DDR3 1.5V供电 |

31,34,44,74,75,128 |

VDD11_SYS |

POWER |

CPU Core电压 |

1.2V供电@600Mhz,1.1V供电@504Mhz |

129 |

GND |

POWER |

- |

GND铜皮全连接,需多加过孔散热 |

50,56 |

NC |

- |

- |

浮空,不能接任何信号 |

引脚 |

功能1 |

功能2 |

功能3 |

功能4 |

功能5 |

功能6 |

功能7 |

功能8 |

|---|---|---|---|---|---|---|---|---|

GPIO A |

||||||||

85 |

PA0 |

GPADC0 |

PSADC0 |

I2C0_SCL |

UART0_TX |

AMIC_IN |

IR_TX |

|

86 |

PA1 |

GPADC1 |

PSADC1 |

I2C0_SDA |

UART0_RX |

AMIC_BIAS |

IR_RX |

|

87 |

PA2 |

GPADC2 |

PSADC2 |

UART0_RTS |

||||

88 |

PA3 |

GPADC3 |

PSADC3 |

UART0_CTS |

||||

89 |

PA4 |

GPADC4 |

PSADC4 |

UART1_TX |

||||

90 |

PA5 |

GPADC5 |

PSADC5 |

UART1_RX |

||||

91 |

PA6 |

GPADC6 |

PSADC6 |

I2C1_SCL |

UART1_RTS |

|||

92 |

PA7 |

GPADC7 |

PSADC7 |

I2C1_SDA |

UART1_CTS |

|||

93 |

PA8 |

RTP_XP |

PSADC8 |

I2C2_SCL |

UART2_TX |

JTAG_DO |

||

94 |

PA9 |

RTP_YP |

PSADC9 |

I2C2_SDA |

UART2_RX |

JTAG_DI |

||

95 |

PA10 |

RTP_XN |

PSADC10 |

I2C3_SCL |

UART2_RTS |

JTAG_MS |

||

96 |

PA11 |

RTP_YN |

PSADC11 |

I2C3_SDA |

UART2_CTS |

JTAG_CK |

||

GPIO B |

||||||||

37 |

PB0 |

SDC0_CMD |

SPI0_HOLD |

I2C1_SCL |

UART7_TX |

|||

38 |

PB1 |

SDC0_CLK |

SPI0_WP |

I2C1_SDA |

UART7_RX |

|||

39 |

PB2 |

SDC0_D3 |

SPI0_CS |

|||||

40 |

PB3 |

SDC0_D0 |

SPI0_MISO |

|||||

42 |

PB4 |

SDC0_D1 |

SPI0_MOSI |

|||||

43 |

PB5 |

SDC0_D2 |

SPI0_CLK |

|||||

45 |

PB6 |

SDC0_D4 |

SPI1_HOLD |

I2C2_SCL |

UART4_TX |

CLK_OUT2 |

||

46 |

PB7 |

SDC0_D5 |

SPI1_WP |

I2C2_SDA |

UART4_RX |

|||

47 |

PB8 |

SDC0_D6 |

SPI1_CS |

UART4_RTS |

UART5_TX |

IR_RX |

||

48 |

PB9 |

SDC0_D7 |

SPI1_MISO |

UART6_RTS |

UART5_RX |

IR_TX |

||

49 |

PB10 |

SDC0_DS |

SPI1_MOSI |

UART6_TX |

||||

51 |

PB11 |

SDC0_RST |

SPI1_CLK |

UART6_RX |

||||

GPIO C |

||||||||

19 |

PC0 |

SDC1_D1 |

LCD_D5 |

SPI2_CLK |

UART1_TX |

JTAG_MS |

PWM0_A |

|

20 |

PC1 |

SDC1_D0 |

LCD_D4 |

SPI2_CS |

UART1_RX |

JTAG_DI |

PWM0_B |

|

21 |

PC2 |

SDC1_CLK |

LCD_D3 |

SPI2_MOSI |

UART1_RTS |

UART0_TX |

PWM1_A |

|

22 |

PC3 |

SDC1_CMD |

LCD_D2 |

SPI2_MISO |

UART2_TX |

JTAG_DO |

PWM1_B |

|

23 |

PC4 |

SDC1_D3 |

LCD_D1 |

UART2_RX |

UART0_RX |

PWM2_A |

||

24 |

PC5 |

SDC1_D2 |

LCD_D0 |

UART2_RTS |

UART3_TX |

JTAG_CK |

PWM2_B |

|

25 |

PC6 |

SDC1_DET |

CLK_OUT0 |

DE_TE |

UART3_RX |

PWM3_A |

||

26 |

PC7 |

UART3_RTS |

PWM3_B |

|||||

GPIO D |

||||||||

18 |

PD0 |

LCD_D0 |

SPI2_CLK |

PBUS_AD0 |

PWM0_A |

|||

17 |

PD1 |

LCD_D1 |

SPI2_CS |

PBUS_AD1 |

PWM0_B |

|||

16 |

PD2 |

LCD_D2 |

SPI2_MOSI |

DE_TE |

PBUS_AD2 |

PWM1_A |

||

15 |

PD3 |

LCD_D3 |

SPI3_CLK |

PBUS_AD3 |

PWM1_B |

|||

14 |

PD4 |

LCD_D4 |

SPI3_CS |

PBUS_AD4 |

PWM2_A |

|||

13 |

PD5 |

LCD_D5 |

SPI3_MOSI |

PBUS_AD5 |

PWM2_B |

|||

12 |

PD6 |

LCD_D6 |

SPI3_MISO |

I2C0_SCL |

UART1_TX |

PBUS_AD6 |

||

11 |

PD7 |

LCD_D7 |

SPI2_MISO |

I2C0_SDA |

UART1_RX |

PBUS_AD7 |

||

10 |

PD8 |

LCD_D8 |

LVDS1_D0N |

SPI1_HOLD |

UART2_TX |

PBUS_AD8 |

EPWM0_A |

|

9 |

PD9 |

LCD_D9 |

LVDS1_D0P |

SPI1_WP |

UART2_RX |

PBUS_AD9 |

EPWM0_B |

|

8 |

PD10 |

LCD_D10 |

LVDS1_D1N |

SPI1_CS |

UART3_TX |

PBUS_AD10 |

EPWM1_A |

|

7 |

PD11 |

LCD_D11 |

LVDS1_D1P |

SPI1_MISO |

UART3_RX |

PBUS_AD11 |

EPWM1_B |

|

6 |

PD12 |

LCD_D12 |

LVDS1_D2N |

SPI1_MOSI |

UART4_TX |

PBUS_AD12 |

EPWM2_A |

|

5 |

PD13 |

LCD_D13 |

LVDS1_D2P |

SPI1_CLK |

UART4_RX |

PBUS_AD13 |

EPWM2_B |

|

4 |

PD14 |

LCD_D14 |

LVDS1_CKN |

SPI3_CLK |

CAP0 |

PBUS_AD14 |

QEP0_H0 |

|

3 |

PD15 |

LCD_D15 |

LVDS1_CKP |

SPI3_CS |

CAP1 |

PBUS_AD15 |

QEP0_H1 |

|

2 |

PD16 |

LCD_D16 |

LVDS1_D3N |

SPI3_MOSI |

CAP2 |

PBUS_CLK |

QEP0_H2 |

|

1 |

PD17 |

LCD_D17 |

LVDS1_D3P |

SPI3_MISO |

PBUS_NCS |

QEP0_A |

||

127 |

PD18 |

LCD_D18 |

LVDS0_D0N |

DSI_D0N |

I2C1_SCL |

PBUS_NADV |

QEP0_B |

|

126 |

PD19 |

LCD_D19 |

LVDS0_D0P |

DSI_D0P |

I2C1_SDA |

PBUS_NWE |

QEP0_I |

|

125 |

PD20 |

LCD_D20 |

LVDS0_D1N |

DSI_D1N |

UART7_TX |

PBUS_NOE |

QEP0_S |

|

124 |

PD21 |

LCD_D21 |

LVDS0_D1P |

DSI_D1P |

UART7_RX |

CLK_OUT0 |

||

123 |

PD22 |

LCD_D22 |

LVDS0_D2N |

DSI_CKN |

I2C3_SCL |

UART6_TX |

||

122 |

PD23 |

LCD_D23 |

LVDS0_D2P |

DSI_CKP |

I2C3_SDA |

UART6_RX |

||

121 |

PD24 |

LCD_DCLK |

LVDS0_CKN |

DSI_D2N |

UART5_TX |

SPI1_CLK |

||

120 |

PD25 |

LCD_HS |

LVDS0_CKP |

DSI_D2P |

UART5_RX |

SPI1_CS |

||

119 |

PD26 |

LCD_VS |

LVDS0_D3N |

DSI_D3N |

PWM3_A |

SPI1_MOSI |

||

118 |

PD27 |

LCD_DE |

LVDS0_D3P |

DSI_D3P |

PWM3_B |

SPI1_MISO |

RTC_32K |

|

GPIO E |

||||||||

52 |

PE0 |

DVP_D0 |

I2C0_SCL |

GMAC0_RXD1 |

EPWM3_A |

PWM0_A |

||

53 |

PE1 |

DVP_D1 |

I2C0_SDA |

GMAC0_RXD0 |

EPWM3_B |

PWM0_B |

||

54 |

PE2 |

DVP_D2 |

CAN0_TX |

UART4_TX |

GMAC0_RXCTL |

EPWM4_A |

PWM1_A |

|

55 |

PE3 |

DVP_D3 |

CAN0_RX |

UART4_RX |

GMAC0_CLKIN |

EPWM4_B |

PWM1_B |

|

58 |

PE4 |

DVP_D4 |

CAN1_TX |

UART5_TX |

GMAC0_TXD1 |

EPWM5_A |

PWM2_A |

|

59 |

PE5 |

DVP_D5 |

CAN1_RX |

UART5_RX |

GMAC0_TXD0 |

EPWM5_B |

PWM2_B |

|

60 |

PE6 |

DSPK0 |

DVP_D6 |

UART5_RTS |

UART6_TX |

GMAC0_TXCK |

QEP1_H0 |

CAP0 |

61 |

PE7 |

DSPK1 |

DVP_D7 |

UART7_RTS |

UART6_RX |

GMAC0_TXCTL |

QEP1_H1 |

CAP1 |

62 |

PE8 |

I2S0_MCLK |

DVP_CK |

UART6_RTS |

UART7_TX |

GMAC0_MDC |

QEP1_H2 |

CAP2 |

63 |

PE9 |

I2S0_BCLK |

DVP_HS |

UART6_CTS |

UART7_RX |

GMAC0_MDIO |

QEP1_A |

|

64 |

PE10 |

I2S0_LRCK |

DVP_VS |

DSPK0 |

CLK_OUT2 |

QEP1_B |

||

65 |

PE11 |

I2S0_DOUT |

I2S0_DIN |

DSPK1 |

CLK_OUT1 |

GMAC0_RXD3 |

QEP1_I |

|

66 |

PE12 |

I2S0_DIN |

SPI3_CLK |

DMIC_CLK |

I2C2_SCL |

GMAC0_RXD2 |

QEP1_S |

|

67 |

PE13 |

SPI3_CS |

DMIC_D0 |

I2C2_SDA |

GMAC0_RXCK |

CAP0 |

||

68 |

PE14 |

SPI3_MOSI |

UART3_TX |

GMAC0_TXD3 |

CAP1 |

|||

69 |

PE15 |

SPI3_MISO |

UART3_RX |

GMAC0_TXD2 |

CAP2 |

|||

70 |

PE16 |

SPI0_CLK |

CAN0_TX |

I2C3_SCL |

GMAC0_TRIG |

|||

71 |

PE17 |

SPI0_CS |

CAN0_RX |

I2C3_SDA |

GMAC0_PPSO |

|||

72 |

PE18 |

SPI0_MOSI |

CAN1_TX |

PWM3_A |

GMAC1_TRIG |

|||

73 |

PE19 |

SPI0_MISO |

CAN1_RX |

PWM3_B |

GMAC1_PPSO |

|||

GPIO F |

||||||||

101 |

PF0 |

SDC2_D1 |

SPI2_CLK |

UART5_TX |

GMAC1_RXD1 |

PBUS_AD0 |

||

102 |

PF1 |

SDC2_D0 |

SPI2_CS |

UART5_RX |

GMAC1_RXD0 |

PBUS_AD1 |

||

103 |

PF2 |

SDC2_CLK |

SPI2_MOSI |

UART5_RTS |

GMAC1_RXCTL |

PBUS_AD2 |

||

104 |

PF3 |

SDC2_CMD |

SPI2_MISO |

UART5_CTS |

GMAC1_CLKIN |

PBUS_AD3 |

||

105 |

PF4 |

SDC2_D3 |

UART6_TX |

GMAC1_TXD1 |

PBUS_AD4 |

|||

106 |

PF5 |

SDC2_D2 |

UART6_RX |

GMAC1_TXD0 |

PBUS_AD5 |

|||

107 |

PF6 |

UART7_TX |

GMAC1_TXCK |

PBUS_AD6 |

||||

108 |

PF7 |

UART7_RX |

GMAC1_TXCTL |

PBUS_AD7 |

||||

109 |

PF8 |

UART7_RTS |

GMAC1_MDC |

PBUS_AD8 |

||||

110 |

PF9 |

UART7_CTS |

GMAC1_MDIO |

PBUS_AD9 |

||||

111 |

PF10 |

I2S1_MCLK |

I2S1_DIN |

UART3_CTS |

CLK_OUT3 |

PBUS_AD10 |

||

112 |

PF11 |

I2S1_BCLK |

PBUS_AD11 |

UART3_TX |

GMAC1_RXD3 |

PBUS_CLK |

||

113 |

PF12 |

I2S1_LRCK |

UART4_RTS |

UART3_RX |

GMAC1_RXD2 |

PBUS_NCS |

||

115 |

PF13 |

I2S1_DOUT |

I2S1_DIN |

UART4_CTS |

UART3_RTS |

GMAC1_RXCK |

PBUS_NADV |

|

116 |

PF14 |

I2S1_DIN |

DSPK0 |

DMIC_D0 |

UART4_TX |

GMAC1_TXD3 |

PBUS_NWE |

|

117 |

PF15 |

DE_TE |

DSPK1 |

DMIC_CLK |

UART4_RX |

GMAC1_TXD2 |

PBUS_NOE |

|

USB |

||||||||

79 |

PU0 |

USB0_DM |

UART0_RX |

UART1_RX |

||||

80 |

PU1 |

USB0_DP |

UART0_TX |

UART1_TX |

||||

81 |

PU2 |

USB1_DM |

UART0_RX |

UART2_RX |

||||

82 |

PU3 |

USB1_DP |

UART0_TX |

UART2_TX |

||||

5.4. 引脚/信号描述¶

引脚/信号名称 |

描述 |

类型 |

|---|---|---|

SYSTEM |

||

RESET |

复位引脚 |

I |

PLL_XI |

24MHz 晶振输入 |

AI |

PLL_XO |

24MHz 晶振输出 |

AO |

RTC |

||

RTC_IO |

RTC 唤醒输出 |

OD |

RTC_VCOIN |

RTC 纽扣电池供电 |

P |

RTC_XO |

32.768KHz晶振输出 |

AO |

RTC_XI |

32.768KHz晶振输入 |

AI |

USB |

||

USB0_DM |

USB0 数据信号负端 |

AI/O |

USB0_DP |

USB0 数据信号正端 |

AI/O |

USB1_DM |

USB1 数据信号负端 |

AI/O |

USB1_DP |

USB1 数据信号正端 |

AI/O |

RTP |

||

RTP_XP |

RTP X方向正端 |

AI |

RTP_YP |

RTP Y方向正端 |

AI |

RTP_XN |

RTP X方向负端 |

AI |

RTP_YN |

RTP Y方向负端 |

AI |

ADC,x = 0~7 |

||

GPADCx |

模拟采样信号输入 |

AI |

ADC,x = 0~11 |

||

PSADCx |

模拟采样信号输入 |

AI |

AMIC |

||

AMIC_IN |

模拟麦克风信号输入 |

AI |

AMIC_BIAS |

模拟麦克风偏压输出 |

AO |

EMAC,x = 0~1 |

||

EMACx_RXD1 |

RMII数据接收信号线1 |

I |

EMACx_RXD0 |

RMII数据接收信号线0 |

I |

EMACx_CRS_DV |

RMII数据接收有效 |

I |

EMACx_REFCLK |

RMII参考时钟 |

I |

EMACx_TXD1 |

RMII数据发送信号线1 |

O |

EMACx_TXD0 |

RMII数据发送信号线0 |

O |

EMACx_TXC |

RMII发送时钟 |

O |

EMACx_TXEN |

RMII数据发送使能 |

O |

EMACx_MDC |

RMII串行管理接口时钟 |

I/O |

EMACx_MDIO |

RMII串行管理接口数据 |

I/O |

CLK_OUTx |

可配置25MHz时钟输出,x = 0~3 |

O |

GMAC,x = 0~1 |

||

GMACx_RXD3 |

RGMII数据接收信号线3 |

I |

GMACx_RXD2 |

RGMII数据接收信号线2 |

I |

GMACx_RXD1 |

RGMII数据接收信号线1 |

I |

GMACx_RXD0 |

RGMII数据接收信号线0 |

I |

GMACx_RXCTL |

RGMII数据接收控制 |

I |

GMACx_CLKIN |

RGMII参考时钟 |

I |

GMACx_TXD3 |

RGMII数据发送信号线3 |

O |

GMACx_TXD2 |

RGMII数据发送信号线2 |

O |

GMACx_TXD1 |

RGMII数据发送信号线1 |

O |

GMACx_TXD0 |

RGMII数据发送信号线0 |

O |

GMACx_TXCK |

RGMII发送时钟 |

O |

GMACx_TXCTL |

RGMII数据发送控制 |

O |

GMACx_MDC |

RGMII串行管理接口时钟 |

I/O |

GMACx_MDIO |

RGMII串行管理接口数据 |

I/O |

PWM,x = 0~3 |

||

PWMx_A |

PWMx A通道 |

O |

PWMx_B |

PWMx B通道 |

O |

EPWM,x = 0~5 |

||

EPWMx_A |

EPWMx A通道 |

O |

EPWMx_B |

EPWMx B通道 |

O |

CAP,x = 0~2 |

||

CAPx |

CAP输入捕获或PWM输出 |

I/O |

QEP,x = 0~1 |

||

QEPn_A |

QEPn 的输入 A 信号 |

I |

QEPn_B |

QEPn 的输入 B 信号 |

I |

QEPn_I |

QEPn 的输入输出 I 信号 |

I/O |

QEPn_S |

QEPn 的输入输出 S 信号 |

I/O |

QEPn_H0 |

QEPn 的霍尔输入信号 A |

I |

QEPn_H1 |

QEPn 的霍尔输入信号 B |

I |

QEPn_H2 |

QEPn 的霍尔输入信号 C |

I |

SPI,x = 0~2 |

||

SPIx_HOLD |

SPIx 保持信号,低电平有效 |

I/O |

SPIx_WP |

SPIx 写保护信号,低电平有效 |

I/O |

SPIx_CS |

SPIx 片选信号,低电平有效 |

I/O |

SPIx_CLK |

SPIx 时钟信号 |

I/O |

SPIx_MOSI |

SPIx 主机数据输出,从机数据输入 |

I/O |

SPIx_MISO |

SPIx 主机数据输入,从机数据输出 |

I/O |

UART,x = 0~7 |

||

UARTx_TX |

UARTx 数据发送 |

O |

UARTx_RX |

UARTx 数据接收 |

I |

UARTx_CTS |

UARTx 发送允许 |

I |

UARTx_RTS |

UARTx 发送请求 |

O |

I2C,x = 0~3 |

||

I2Cx_SCL |

I2Cx 串行时钟信号 |

I/O |

I2Cx_SDA |

I2Cx 串行数据信号 |

I/O |

CIR |

||

IR_TX |

红外数据发送 |

O |

IR_RX |

红外数据接收 |

I |

I2S,x = 0~1 |

||

I2Sx_MCLK |

I2Sx 主时钟 |

O |

I2Sx_LRCK |

I2Sx 左/右时钟 |

I/O |

I2Sx_BCLK |

I2Sx 位时钟 |

I/O |

I2Sx_DOUT |

I2Sx 串行数据输出 |

O |

I2Sx_DIN |

I2Sx 串行数据输入 |

I |

DSPK |

||

DSPK0 |

Speaker 信号输出通道0 |

I/O |

DSPK1 |

Speaker 信号输出通道1 |

I/O |

SDC,x = 0~2 |

||

SDCx_CMD |

SDC0 控制信号 |

I/O |

SDCx_CLK |

SDC0 时钟信号 |

O |

SDCx_D[3:0] |

SDC0 数据输入输出 |

I/O |

LCD |

||

LCD_D[23:0] |

LCD 数据输出 |

O |

LCD_DCLK |

LCD 时钟信号 |

O |

LCD_HS |

LCD 行场同步 |

O |

LCD_VS |

LCD 列场同步 |

O |

LCD_DE |

LCD 数据使能 |

O |

LVDS,x = 0~1 |

||

LVDSx_CKN |

LVDSx 时钟负端 |

AI |

LVDSx_CKP |

LVDSx 时钟正端 |

AI |

LVDSx_D0N |

LVDSx 数据0负端 |

AI |

LVDSx_D0P |

LVDSx 数据0正端 |

AI |

LVDSx_D1N |

LVDSx 数据1负端 |

AI |

LVDSx_D1P |

LVDSx 数据1正端 |

AI |

LVDSx_D2N |

LVDSx 数据2负端 |

AI |

LVDSx_D2P |

LVDSx 数据2正端 |

AI |

LVDSx_D3N |

LVDSx 数据3负端 |

AI |

LVDSx_D3P |

LVDSx 数据3正端 |

AI |

MIPI DSI |

||

DSI_CKN |

MIPI DSI 时钟负端 |

AI |

DSI_CKP |

MIPI DSI 时钟正端 |

AI |

DSI_D0N |

MIPI DSI 数据0负端 |

AI |

DSI_D0P |

MIPI DSI 数据0正端 |

AI |

DSI_D1N |

MIPI DSI 数据1负端 |

AI |

DSI_D1P |

MIPI DSI 数据1正端 |

AI |

DSI_D2N |

MIPI DSI 数据2负端 |

AI |

DSI_D2P |

MIPI DSI 数据2正端 |

AI |

DSI_D3N |

MIPI DSI 数据3负端 |

AI |

DSI_D3P |

MIPI DSI 数据3正端 |

AI |

DVP |

||

DVP_CK |

DVP 像素时钟 |

I |

DVP_HS |

DVP 行场同步 |

I |

DVP_VS |

DVP 列场同步 |

I |

DVP_D[7:0] |

DVP 数据输入 |

I |

PBUS |

||

PBUS_CLK |

PBUS 外部总线时钟信号 |

O |

PBUS_NCS |

PBUS 外设片选信号,低电平有效 |

O |

PBUS_NADV |

PBUS 总线地址有效信号,低电平有效 |

O |

PBUS_NWE |

PBUS 总线读写控制信号,低电平为写,高电平为读 |

O |

PBUS_NOE |

PBUS 外设输出使能信号,低电平有效 |

O |

PBUS_AD[15:0] |

PBUS 地址/数据总线 |

I/O |